# 6.002 - Lecture 02

(Brute Force) Circuit Analysis

- Review: Labeling Devices

- Review: Nodes and Loops

- Brute Force Analysis

- Series and Parallel Resistors

- Voltage and Current Dividers

# Circuit Terminology

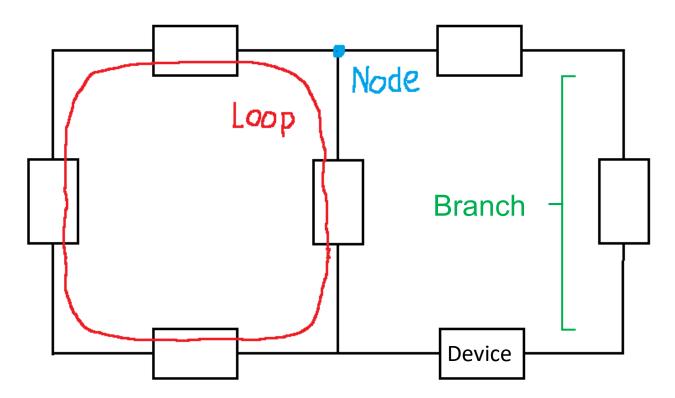

**Device:** a multi-terminal lumped-parameter piece of electrical hardware having identifiable voltages across (between) its terminals and currents through its terminals. Most devices in 6.200 have only two terminals.

**Circuit:** a collection of devices joined together at their terminals, presumably designed for a useful purpose.

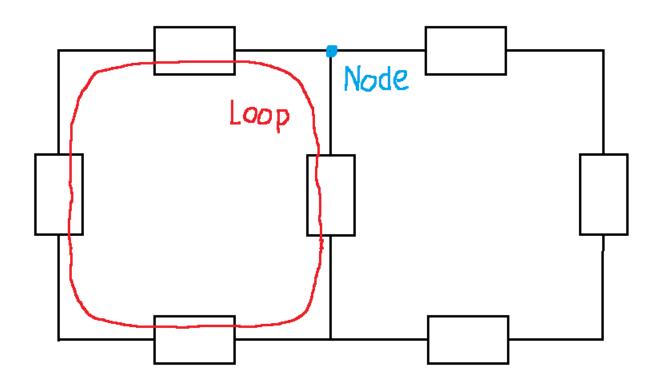

**Node:** the topological point at which one or more device terminals are joined together. Nodes can be spatially distributed, occupying more than a point in real space.

**Branch:** the topological pathway between two electrically neighboring nodes. Branches are occupied by devices.

**Loop:** A closed-path through the branches that traverses no branch more than once.

**Circuit Analysis:** determination of all branch (device) voltages and currents.

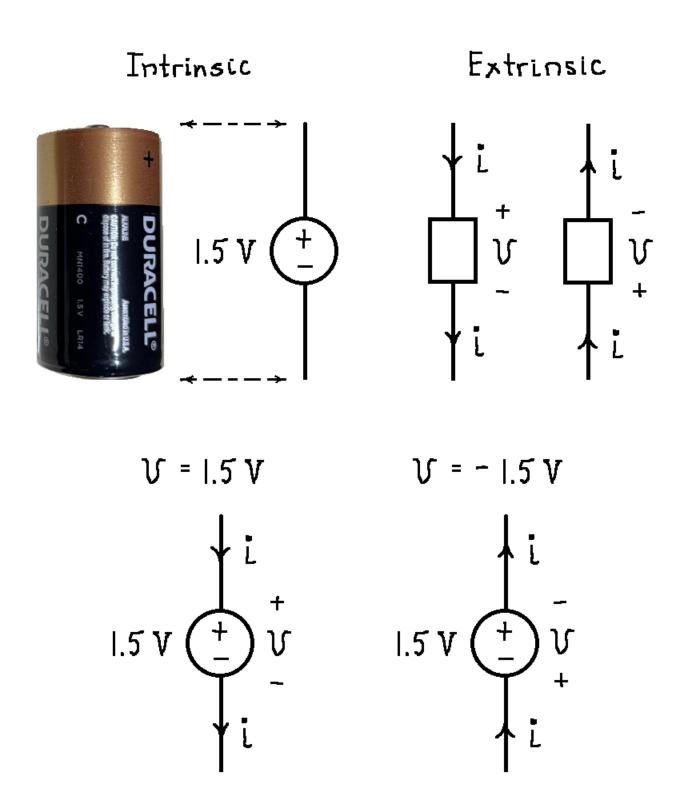

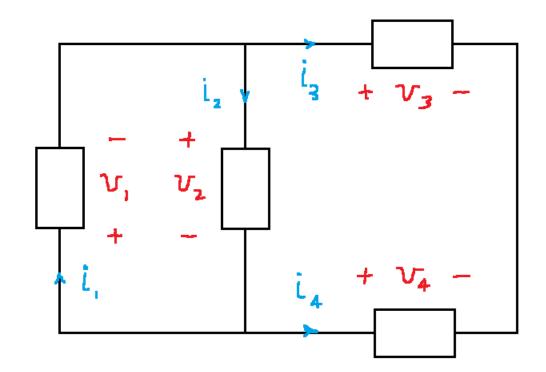

#### Labeling

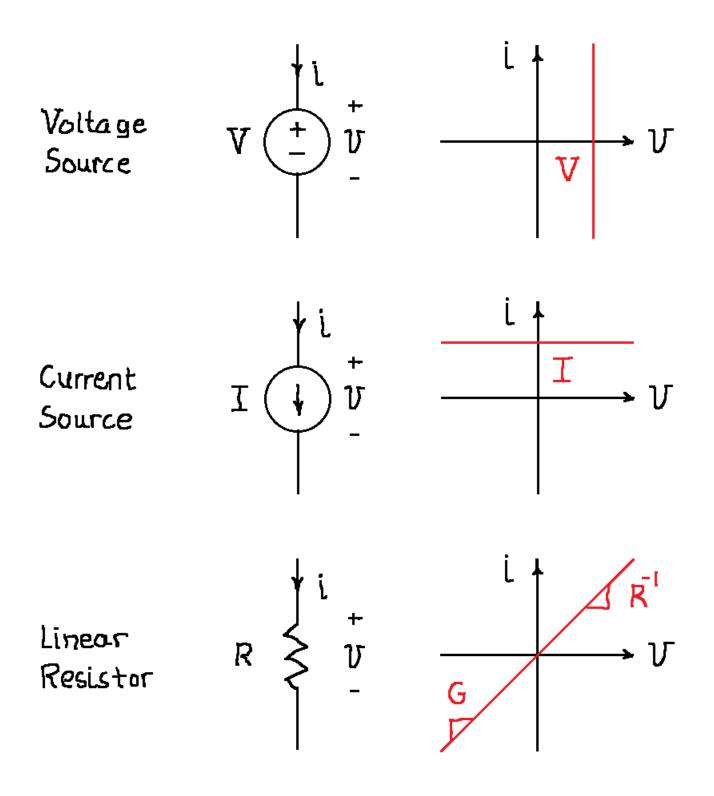

**Devices**

### **Connections**

KVL: ∑び=0 Around - Either Loop Direction

KCL: Σi=0 Into - Or Out Node - From

#### <u>KVL & KCL</u>

$\begin{array}{l} \mathsf{KVL}: \ \cdot \ \mathbf{V_1} \ \cdot \ \mathbf{V_2} \ = \ 0 \ \text{ or } \ \mathbf{V_1} \ = \ - \ \mathbf{V_2} \\ & \mathbf{V_4} \ + \ \mathbf{V_2} \ - \ \mathbf{V_3} \ = \ 0 \ \text{ or } \ \mathbf{V_4} \ + \ \mathbf{V_2} \ = \ \mathbf{V_3} \\ & - \ \mathbf{V_1} \ - \ \mathbf{V_3} \ + \ \mathbf{V_4} \ = \ 0 \ \text{ or } \ \mathbf{V_4} \ = \ \mathbf{V_1} \ + \ \mathbf{V_3} \\ & \mathsf{KCL} \ : \ \mathbf{i_1} \ - \ \mathbf{i_2} \ - \ \mathbf{i_3} \ = \ 0 \ \text{ or } \ \mathbf{i_1} \ = \ \mathbf{i_2} \ + \ \mathbf{i_3} \\ & \mathbf{i_3} \ + \ \mathbf{i_4} \ = \ 0 \ \text{ or } \ \mathbf{i_3} \ = \ - \ \mathbf{i_4} \\ & - \ \mathbf{i_1} \ + \ \mathbf{i_2} \ - \ \mathbf{i_4} \ = \ 0 \ \text{ or } \ \mathbf{i_2} \ = \ \mathbf{i_1} \ + \ \mathbf{i_4} \end{array}$

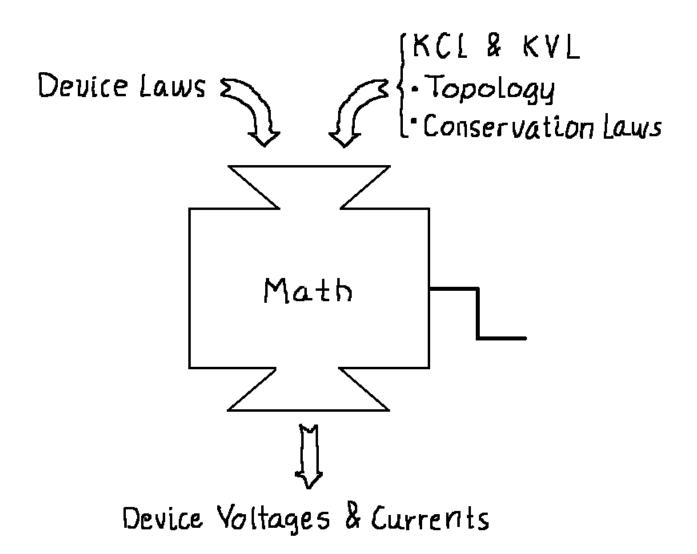

#### **Brute Force Analysis**

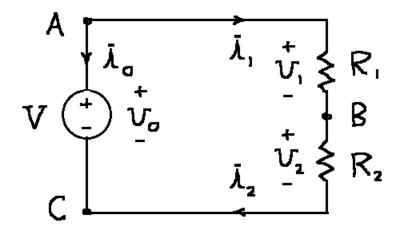

#### Brute Force Analysis #1

$\frac{Solution}{i_{1} = i_{2} = -i_{0} = V/(R_{1}+R_{2}) = i$   $v_{0} = V ; v_{1} = R_{1}i = V \frac{R_{1}}{R_{1}+R_{2}} ; v_{2} = R_{2}i = V \frac{R_{2}}{R_{1}+R_{2}}$ Note:  $v_{0} = v_{1}+v_{2} = \lambda(R_{1}+R_{2}) \Rightarrow \frac{v_{0}}{i} = \frac{R_{1}+R_{2}}{E#fective R}$

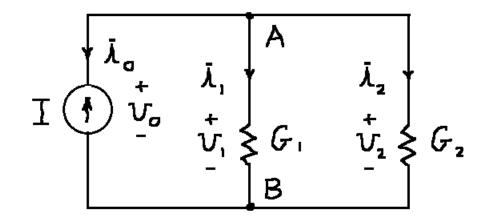

#### Brute Force Analysis #2

# $\frac{Solution}{V_0 = V_1 = V_2} = \frac{I}{(G_1 + G_2)} = V$ $i_0 = -I; \quad i_1 = G, V = \frac{I}{G_1} = \frac{G_2}{G_1 + G_2}; \quad i_2 = GV_2 = \frac{I}{G_2} = \frac{G_2}{G_1 + G_2}$ Note: $-i_0 = i_1 + i_2 = V(G_1 + G_2) = \frac{V}{-i_0} = \frac{G_1 + G_2}{Effective}$

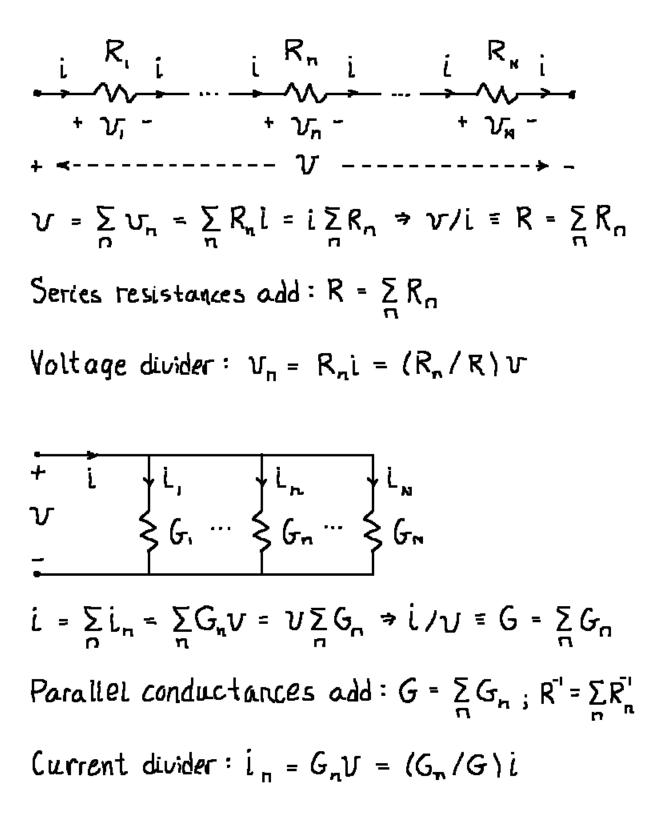

#### Resistor Combinations

## <u>Summary</u>

- Intrinsic and extrinsic labels

- Brute force analysis

- Series resistances add

- Parallel conductances add

- Voltage dividers

- Current dividers